#### Finkenstraße 48 70199 Stuttgart

Tel: +49 - (0)711 - 60 19 637 FAX: +49 - (0)711 - 60 19 638 Mail: post@inventronik.de Internet: www.inventronik.de

# Viplax-I

# **Users Manual**

Viplax-I Transmitter- / Receiver Unit

# Table of Contents

| Introduction                                                 | 8  |

|--------------------------------------------------------------|----|

| Safety Restrictions                                          | 8  |

| General Description of the Viplax-I Transmission System      | 9  |

| Shipping List                                                | 9  |

| Accessories                                                  | 9  |

| Viplax-I Transmitter (Handheld version)                      | 11 |

| Technical Description                                        | 11 |

| Adjustment of the gain factor                                | 12 |

| Adjustment of the Window Comparators of the Transmitter      | 14 |

| Default Switch Settings:                                     | 16 |

| Visualisation                                                | 16 |

| Auxiliary Port                                               | 17 |

| Power supply                                                 |    |

| Maintenance of the Transmitter                               | 19 |

| Viplax-I Transmitter (Eurocard version)                      | 20 |

| The Orientation of the Comparator DIP switches               | 20 |

| The used Power Supply                                        | 20 |

| Additional I/O                                               | 21 |

| Analog Input or Sensor Plug                                  | 22 |

| Viplax-I Receiver                                            |    |

| Technical Description                                        | 23 |

| Functional Description of the Error Logic                    | 24 |

| Error Processing System                                      | 24 |

| Link Synchronisation                                         | 24 |

| First Fault Memory                                           | 25 |

| Signal LEDs                                                  | 28 |

| Digital Interface                                            | 28 |

| Digital I/O-Ports                                            | 29 |

| Power Supply for the Receiver                                | 30 |

| Power Up Sequence                                            | 30 |

| Maintenance of the Receiver                                  |    |

| Maintenance of the Transmission System                       | 31 |

| Offset Calibration                                           | 31 |

| Viplax-I Service-Software                                    | 32 |

| Viplax-I Interface Options                                   |    |

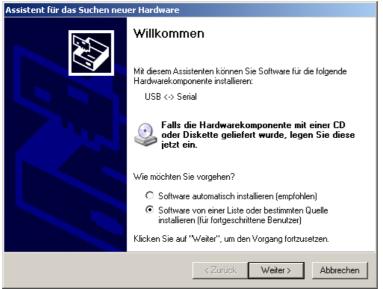

| USB Option: Installing a Driver for a Virtual USB/RS232 Port | 32 |

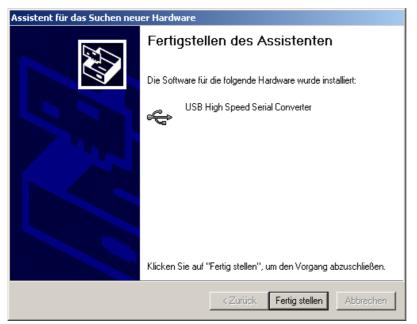

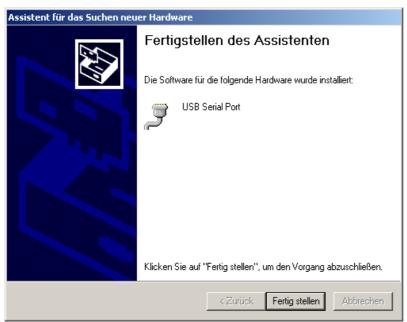

| Screenshots of the Installation Process                      | 33 |

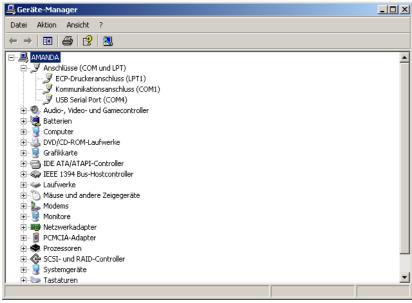

| Verifying the COM-Ports                                      | 35 |

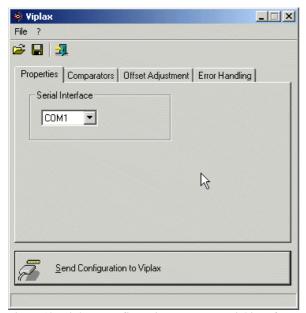

| Viplax-I Configuration Program                               | 35 |

| TCP/IP Ethernet-Interface:                                   |    |

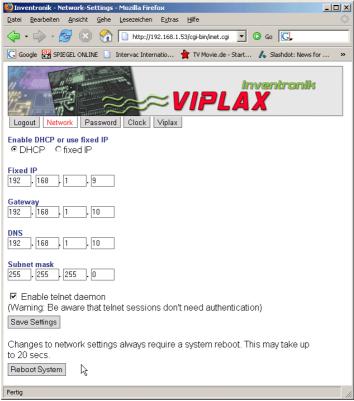

| Using a Web-Browser for Viplax-I Configuration               | 38 |

| Overview                                                     | 38 |

| Getting started                                              | 38 |

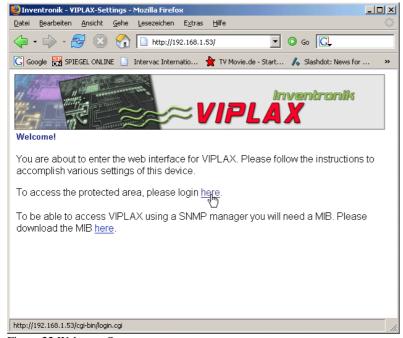

| Viplax-I Start Page                                          | 39 |

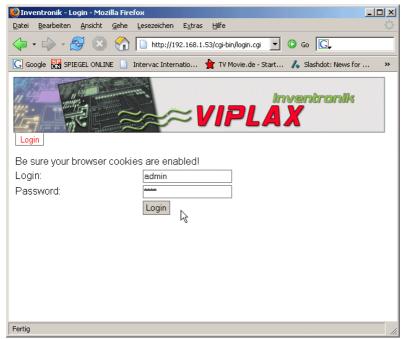

| Viplax-I Login (HTTP-Authentication)                         | 40 |

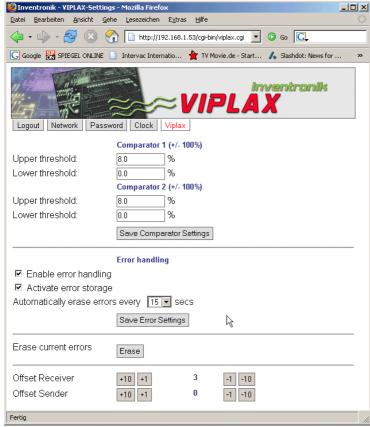

| Viplax-I Specific Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

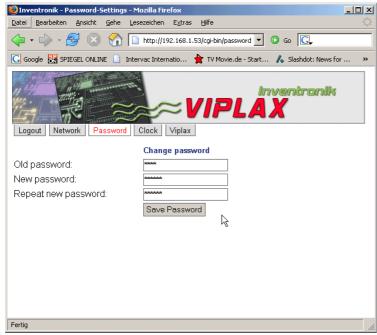

| Change Password                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Network Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| TCP/IP Protocol SNMP (Simple Network Management Protocol)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| Changing the FPGA-Configware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

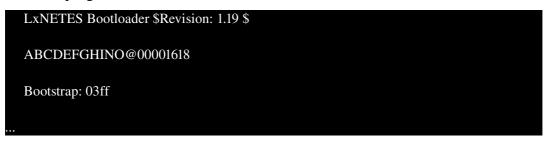

| Changing the Microcontroller Firmware (MiniFlex only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| Appendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Technical Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| Transmitter_V3_RevA, Receiver_V3_RevA:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |

| Connector Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| Test Procedure for Transmitter and Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Transmitter Functional Tests:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Receiver Functional Tests:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| Printed circuit diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

| Accessories                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Receiver Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

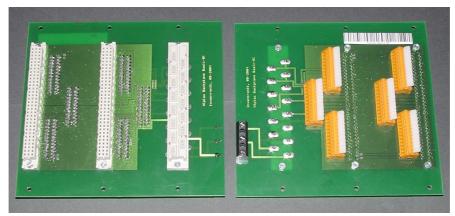

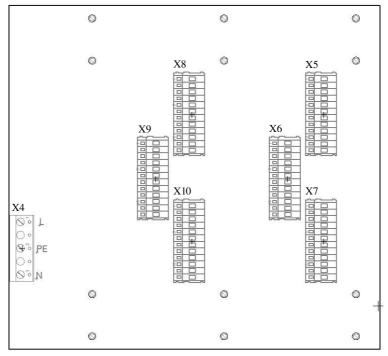

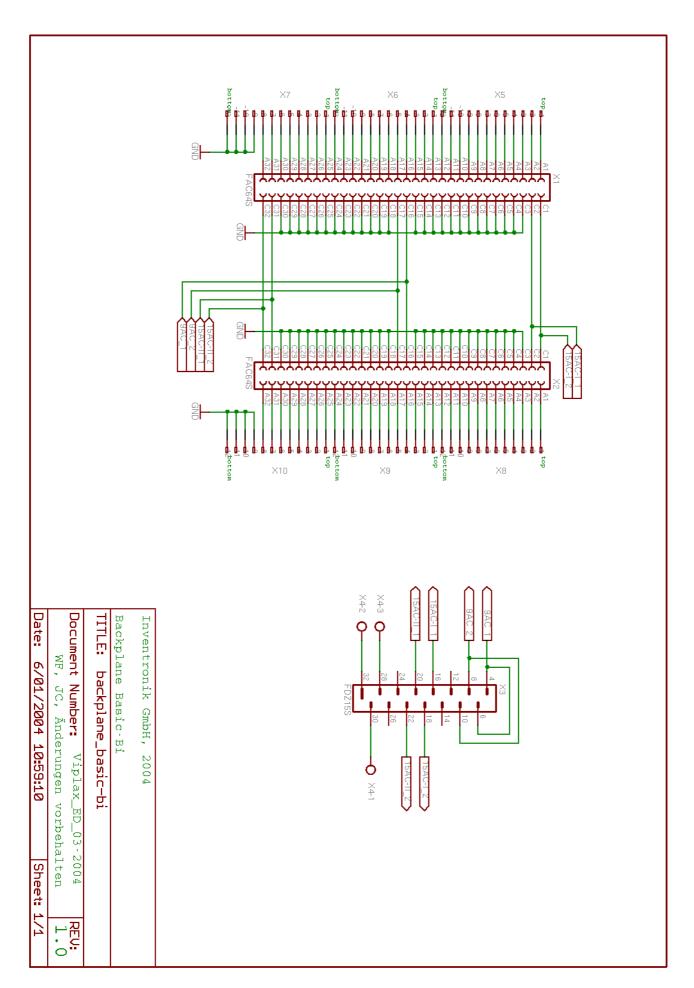

| Backplane Basic and Basic-Bi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| Repair                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61             |

| Mobile Trades                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Table Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ut voltage for |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sware not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sware not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26                                                                                                                                                                                                                                                                                                                                                                                                                                                | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27                                                                                                                                                                                                                                                                                                                                                                                                   | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27                                                                                                                                                                                                                                                                                                                                                   | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28                                                                                                                                                                                                                                                                                             | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28                                                                                                                                                                                                                                     | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29                                                                                                                                                          | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29  Table 16: Connector SV1; Receiver. 49                                                                                                                   | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29  Table 16: Connector SV1; Receiver. 49  Table 17: Connector SV2; Receiver. 49                                                                            | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29  Table 16: Connector SV1; Receiver. 49  Table 18: Connector X5; Receiver. 50                                                                             | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29  Table 16: Connector SV1; Receiver. 49  Table 18: Connector X5; Receiver. 49  Table 19: Connector X5; Receiver. 50  Table 19: Connector X6; Receiver. 51 | _              |

| Table 1: Selectable gain factors and the resulting total gain v over the maximum inp the transmitter revision C and revision C10. 12  Table 2: Adjustment of the comparator functionality via SW2. Remark: All other sw are not used 14  Table 3: Factory settings of the DIP-switches. 15  table 4: Auxiliary port – Lemo header. 16  table 5: Auxiliary port – 10 pin header. 16  table 6: Power supply. 17  Table 7: Additional I/O 20  table 8: Front panel female plug. 21  Table 9: Error Signals wired to the connector X5. 26  Table 10: Error Signals wired to the connector X10. 26  Table 11: Signalisation of the USB type. 27  Table 12: Signalisation of the TCP/IP type. 27  Table 13: Digital Data wired to the connector X5. 28  Table 14: Digital Interface wired to connector X11. 28  Table 15: Supply voltages for the receiver connected via connector X5. 29  Table 16: Connector SV1; Receiver. 49  Table 18: Connector X5; Receiver. 50                                                                             | _              |

Table 23: Connector SV2; Transmitter. 52

Table 24: Pinout of the power supply connector. 74

Table 25: Pin-out of the Terminals X5 to X10 of the Backplane. 77

#### Figure Index

```

Figure 1: Viplax-ITransmitter (handheld version). 11

Figure 2: Board Layout of the Viplax-I Transmitter (Handheld Version): DIP-switches for gain

adjustments and the comperator.

12

Figure 3: Disassembly of the transmitter PCB to the left side!

Figure 4: GAIN adjustment of the Viplax-ITransmitter via DIP-switches.

13

figure 5: COMP-SEL SW2 and CMP-LVL SW1 of the Viplax-ITransmitter.

Figure 6: Lemo 5B-2 17

Figure 7: Lemo 0B-2 18

Figure 8: mechanical Layout of the stand alone transmitter power supply 18

Figure 9: Orientation of the comparator DIP switches

Figure 10: Lemo 5B-2

Figure 11: Viplax-IReceiver.

Figure 12: Viplax-I Receiver (front view). 26

Figure 13: Windows hardware facility assistant

33

Figure 14: Selection of the driver directory 33

Figure 15: Finish the driver installation; Serial converter

Figure 16: Finish the driver installation; USB serial port driver

34

Figure 17: USB Serial Port (COMx) 35

Figure 18: Viplax-I configuration program, serial interface 35

Figure 19: Viplax-I configuration program, thresholds

Figure 20: Viplax-I configuration program, error handling 36

Figure 21: Viplax-I configuration program, offset adjustments

37

Figure 22: Welcome-Screen 39

Figure 23: User Authentication

40

Figure 24: Viplax-IAdjustments

40

Figure 25: Change password 41

Figure 26: Viplax-INetwork settings

42

Figure 27:

75

Figure 28:

75

Figure 29: Front- und Rear-view of the Backplane Basic-Bi

77

Figure 30: Backplane Basic-Bi rear view

```

# History

| Issue | Date     | Reason For Changes                                                 |

|-------|----------|--------------------------------------------------------------------|

| 01    | 20040517 | Initial issue.                                                     |

| 02    | 20040603 | Added schematics and PCBs.                                         |

| 03    | 20050601 | English Version.                                                   |

| 04    | 20051115 | Minor corrections.                                                 |

| 05    | 20060402 | New case type and different connectors (optional).                 |

| 06    | 20060925 | Added adjustment of the gain for the transmitter C10.              |

| 07    | 20060925 | The BNC output has up to now a maximum amplitude of 10V at 50 Ohm. |

| 08    | 20060925 | Updated technical data.                                            |

| 09    | 20060925 | Added resynchronisation state machine feature.                     |

| 10    | 20060925 | Correction of the figure index.                                    |

| 11    | 20061114 | Changed testing behaviour.                                         |

| 12    | 20061114 | Removed outdated schematics.                                       |

### References

[1]

# Introduction

Ladies and Gentlemen,

Thank you for purchasing Viplax-I from Inventronik GmbH. With the purchase of this product you have acquired a high-quality Analog-Signal transportation system. Please read this user manual completely before start-up. This document will give you comprehensive information regarding Viplax-I capabilities and how you can most efficiently use them. Inventronik GmbH is endeavored to keep the most current information concerning our products at your disposal. On our website (www.inventronik.de) the newest documents are available for you to download.

# Safety Restrictions

Inventronik GmbH is proud to supply you with a high-quality device, nevertheless we cannot guarantee that this module works under all possible conditions without failure. Do not use this product in applications, where damage in the module could lead to direct danger for humans, e.g. medical systems, protection devices and such.

Inventronik GmbH cannot be held in any way responsible for general or specific damages caused by abuse or misuse of our products.

This product is conceived exclusively for use with the specified voltages. We recommend the use of the Viplax-I power supply. Higher voltages can lead to malfunction and/or the total loss of the module. **Please only use certified power supplies.**

# General Description of the Viplax-I Transmission System

Viplax-I is a system designed for transmitting analog bipolar signals with little regard to the difference in electrical potential. Electrical isolation has been accomplished by using a fiber optic line between transmitter and receiver. The analog input signal on one end is converted to a digital signal, serialized and sent via highspeed fiber optic link to the receiver unit.

The receiver unit reverses the process, converting the serial data with mimimal delay and extreme accuracy back into the analog signal measured by the transmitter.

A high-quality, low-impedance output-driver delivers the recovered analog signal to loads with small impedance e.g. correctly terminated coaxial cables at 50 or 75 Ohm. The digital resolution of the system is 14 bit. The analog bandwidth lies at about 2.5MHz (3dB).

Besides the analog data transmission there are additional features distinguishing Viplax-I from other commercial systems. For instance, digital data processing, fast and accurate comparator functions, comfortable software, easy offset calibration, and support for software or hardware add-ons.

For further information regarding these additional features please refer to the dedicated chapters in this document.

# **Shipping List**

A standard set of Viplax-I transmission systems consists of the following components:

- A transmitter unit: Viplax-I Transmitter.

- A power supply.

- A fiber optic line with a length of 2m (other lengths are available on request).

- A receiver unit.

- For configuration: a 1 meter USB or TCP/IP cable (depending on the type of receiver).

- CD-Rom with datasheets, circuit diagrams, documentation and system software.

#### **Accessories**

Currently available accessories for Viplax-I:

- Power supply for the receiver: 3U, 14HU plug in unit for 19" rack mount systems.

- Fiber optic links: custom lengths

- USB or TCP/IP interface cables in several lengths.

- Backplane Basic: backplane for 19 inch 3U systems. This printed circuit board wires a Viplax-I receiver power supply with one receiver.

- Backplane Basic-Bi: backplane für 19 inch 3U systems. This printed circuit board wires a Viplax-I receiver power supply with two receivers.

If you have need of special equipment please contact Inventronik GmbH (<u>www.inventronik.de</u>).

# Viplax-I Transmitter (Handheld version)

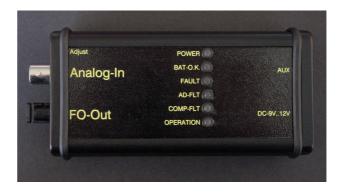

Figure 1: Viplax-ITransmitter (handheld version).

#### **Technical Description**

The Viplax-I transmitter has two different case options. The a 3U unit is for 19" rack-mount systems and the compact, high frequency resistant, metal case, is suited for high voltage applications. There are only a few adjustments, and three cables necessary to operate the transmitter unit. The following description is specifically for the handheld version, but the 3U 19" version operates the same way, except the power supply is connected via a backplane Basic or Basic-Bi.

The transmitter is a powerful unit, compact, easy-to-install and maintenance free thanks to the use of modern electronic components. It's main elements are; a high quality analog digital converter with high resolution, a modern Field Programmable Gate Array (FPGA), a high-speed bitstream converter and a high-speed optical transmitter unit.

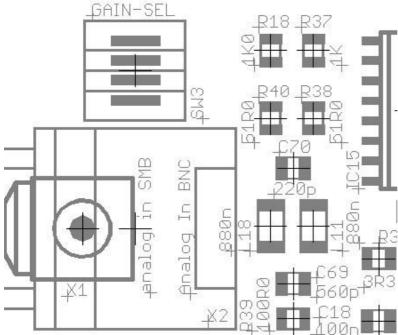

The data processing in the transmitter unit functions as follows: a BNC or SMB-jack connects the analog input signal. One or the other is available for the handheld unit, both for the rack mount version. An input amplifier with 1MOhm input impedance has gain factors of 1.0; 2.0; 5.0 and 10.0. The selection of the desired gain factor is done via DIP-switches (Figure 2).

To avoid signal distortion through aliasing effects there is a 'Bessel' filter of 5<sup>th</sup> order (30dB/octave) between the preamplifier and the analog digital converter.

The AD converter has a resolution of 14bit and a sampling rate of 10 MSps transmitting analog signals with a bandwidth of 2.5MHz.

In addition to the AD payload there are four system check bits to transmit. The status of the power supply, the AD converter overflow bit, the comparator status and a freely usable FLAG "GP\_BIT7", which is connected to pin 9 of the auxiliary port.

Finally all parallel digital data are serialized, transmission check bits are generated and send through high speed optical link.

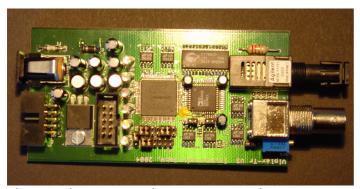

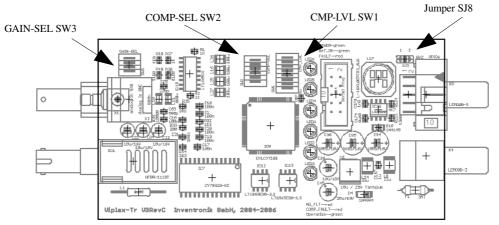

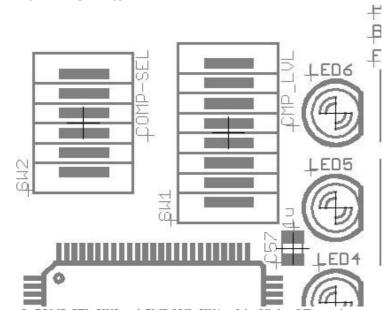

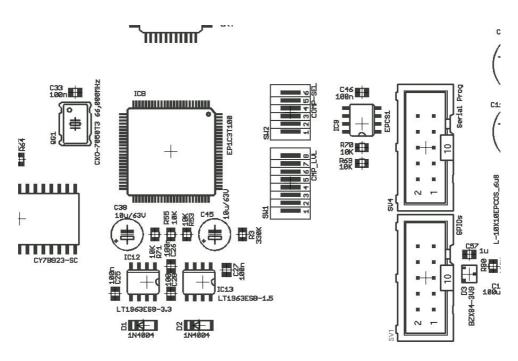

Figure 2: Board Layout of the Viplax-I Transmitter (Handheld Version): DIP-switches for gain adjustments and the comperator.

### Adjustment of the gain factor

**Important notice:** *Do not try to remove the board from the right side of the case!* This may damage either the case or the circuit board.

The only way to remove the circuit board from the handheld case is as shown in the figure below.

Figure 3: Disassembly of the transmitter PCB to the left side!

The first step is to disassemble the circuit board from it's case. Remove the cap which covers the BNC/SMB jack and the ST jack on the left side of the fiber optic transmitter. Afterwards position the board as shown in figure 2 and you will find the gain DIP switches (GAIN\_SEL SW3) in the upper left corner right above the BNC/SMB connector.

Figure 4: GAIN adjustment of the Viplax-I Transmitter via DIP-switches.

The adjustment of the gain factor is for the Viplax handheld transmitter revision C and for the Viplax handheld transmitter revision C10 slightly different. The version of the transmitter is labeled on the top of the printed circuit board as follows:

Viplax-Tr V3RevC for the revision C type and

**Viplax-Tr V3RevC10** for the revision C10 type.

As the transmitter revision C provides four gain factors selectable via the switch 3 (GAIN-SEL), the transmitter revision C10 provides three gain factors and one attenuator selectable via GAIN-SEL.

The gain *v* is adjusted for the preamplifier by GAIN-SEL SW3 (see figure 4). Only one switch of the gain select switches must be turned on. Additionally, the attenuator switch may be turned on. In rows 4 and 5 of Table 1 the gain factors of the Viplax-I system (transmitter-receiver) are referenced to the analog outputs (BNC/SMB) of the receiver.

The output, connected to the BNC jack has a maximum amplitude of +/- 10V, and the SMB jack has an amplitude of +/- 10V. The different gain factors are adjustable as follows:

| SW3:                               | 1 - On | 2 - On | 3 - On | 4 – On Revision C | 4 - Revision C10:   |

|------------------------------------|--------|--------|--------|-------------------|---------------------|

| $U_{inmax}$                        | ±10.0V | ±5.0V  | ±2.0V  | ±1V               | on = :1<br>off= :10 |

| v                                  | 1.0    | 2.0    | 5.0    | 10.0              | on = :1<br>off= :10 |

| U <sub>in</sub> / U <sub>BNC</sub> | 1.0    | 2.0    | 5.0    | 10.0              | on = :1<br>off= :10 |

| U <sub>in</sub> / U <sub>SMB</sub> | 1.0    | 2.0    | 5.0    | 10.0              | on = :1<br>off= :10 |

Table 1: Selectable gain factors and the resulting total gain v over the maximum input voltage for the transmitter revision C and revision C10.

The maximum input voltage must not exceed 10V for the transmitter revision C and revision C10 with no attenuation and not exceed 50V for the revision C10 with attenuation! The attenuation is 'on', when Switch 4 is off.

#### **Adjustment of the Window Comparators of the Transmitter**

The absolute value of the comparator threshold is configured through DIP-switches CMP-LVL SW1 (see figures 2 and 5). The switch block is located above the FPGA (big square chip). Adjustment of the threshold is achieved in steps of 1%. Using the switches as 7bit binary, you need to encode the desired value. A switch in on position means a logic '1' and in off position a logic '0'. The switch labeled "1" is the least significant bit (LSB) and "7" is the most significant bit (MSB) of the 7 bit code. Important: Switch 8 of switch block SW1 is used to enable the comparator (On = enable). Factory setting is Off!

figure 5: COMP-SEL SW2 and CMP-LVL SW1 of the Viplax-I Transmitter.

Example: A threshold of 67% has a pattern of "On, Off, Off, Off, Off, On, On" (100011 = decimal 67).

Since there is a maximum of 127% adjustable, all values greater 100% are interpreted as 100%. The threshold value may be used for positive and negative comparator values. A threshold setting of 100% equals an A/D input signal of exactly 2.5V (absolute value). This means that the preamplified input signal must not exceed this value not to produce a A/D converter overflow or wrong comparator behaviour. With the switches COMP-SEL SW2 there are negative, positive or both comparators selectable (see Table 2).

| SW2 (2+1) | Description                                                          |

|-----------|----------------------------------------------------------------------|

| On/On     | Comparator detects overstepping of positive and negative thresholds. |

| On/Off    | Comparator detects overstepping of positive thresholds only.         |

| Off/On    | Comparator detects overstepping of negative thresholds only.         |

| Off/Off   | not used                                                             |

Table 2: Adjustment of the comparator functionality via SW2. Remark: All other switches of SW2 are not used

Transmitter comparators are helpful if you want to supervise the input signal directly at the transmitter case. Otherwise we recommend to use the more powerful receiver comparators. These comparators allow easy adjustment through PC integration.

#### **Default Switch Settings:**

The transmitter factory settings for the DIP-switches SW1-SW3:

| Jumper:   | Adjustment                     | Remarks                                 |

|-----------|--------------------------------|-----------------------------------------|

| SW1 (7-1) | Off, On, On, Off, Off, On, Off | 50,00%                                  |

| SW2 (2-1) | On, On                         | both, positive and negative supervision |

| SW3 (4-1) | x1 (Off, Off, Off, On)         | gain set to factor 1                    |

| SW1 (8)   | Off                            | comparator inactive                     |

Table 3: Factory settings of the DIP-switches.

#### **Visualisation**

Six LEDs are located on the top cover of Viplax-I transmitter (handheld version). All LEDs are used for status and error indication:

- 1. POWER: power status. This LED indicates the correct function of the internal charge pump. The charge pump is used to create the negative voltage supply. The LED may be darker than the other to avoid unnecessary load of the charge pump.

- 2. BAT-O.K.: voltage supervision control. You may use a battery to power the Viplax-I transmitter. This LED detects its correct charge condition. If the transmitter is operated by a power supply, the LED statically is turned on.

- 3. FAULT: collective error. It indicates either a comparator threshold or an AD converter overflow error.

- 4. AD-FLT: overflow error of the AD converter. This LED indicates if the AD converter is driven into saturation by too high input signals. Solution is to reduce the input voltage or the amplification factor.

- 5. COMP-FLT: comparator threshold event. The LED indicates the input voltage falls outside of the adjusted thresholds.

- 6. OPERATION: indicates steady operation, a well initialized transmitter without system faults or other errors (no comparator- or AD converter errors and battery in good charge condition).

### **Auxiliary Port**

The Viplax-I transmitter unit (handheld type) is equipped with a 10 pin auxiliary port header or optionally with a 5 pin Lemo 0B female plug. Both carries the 9V..12V operating voltage, GND and some user defined input/output lines. The signals are dedicated for system enhancements (please contact Inventronik GmbH for usage).

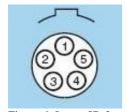

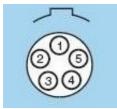

The port connector Lemo 0B-5. It is located right behind the right panel (Figure 2). Figure 6 shows the front view on the handheld case.

Figure 6: Lemo 5B-2

| Pin 1 | Gnd                       |

|-------|---------------------------|

| Pin 2 | GPIO 1                    |

| Pin 3 | GPIO 2                    |

| Pin 4 | Vcc (9V12V) or GPIO 3 (1) |

| Pin 5 | Monitor (2)               |

table 4: Auxiliary port – Lemo header.

- (2) GPIO3 is the output signal of the digital comparator. It can be accessed by connecting the jumper SJ8 to position 2. The VCC output on this pin is selected by connecting the jumper SJ8 to position 1. For detailed information see the printed circuit layout and the schematics in this document or contact nventronik GmbH.

- (2) Is a mirror of the input signal equipped with an impedance converter with a max. output voltage of 2.5V (max. output current 20mA).

The pin header (10 pin) is also located right behind the right panel (Figure 2). The table 5 shows the pinout of this header.

| Pin 1 | GPIO 1                       | Pin 6  | GPIO 5                       |

|-------|------------------------------|--------|------------------------------|

| Pin 2 | GND                          | Pin 7  | GPIO 6                       |

| Pin 3 | GPIO 2                       | Pin 8  | GPIO 7                       |

| Pin 4 | <b>GPIO</b> 3 <sub>(1)</sub> | Pin 9  | GPIO 8                       |

| Pin 5 | GPIO 4                       | Pin 10 | <i>VCCIO</i> (3,3 <i>V</i> ) |

table 5: Auxiliary port – 10 pin header.

<sup>(1)</sup> GPIO3 is the output signal of the digital comparator. For detailed information see the printed circuit layout and the schematics in this document or contact nventronik GmbH.

### **Power supply**

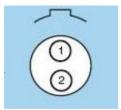

The power supply with 9V...12V DC is used to power the Viplax-I transmitter (part of the delivery). The recommended setting is 9V. The connector type is Lemo 0B-2. Figure 7 shows the front view.

| Pin 1 | Vcc (9V12V) |

|-------|-------------|

| Pin 2 | Gnd         |

table 6: Power supply.

Figure 7: Lemo 0B-2

The transmitter provides an optimized voltage control system to ease the use of a backup battery. Supervision of the battery charge condition is accomplished by a comparator. This status information is also available to the receiver unit.

The delivered power supply is build in 50Hz technique. We do not recommend other power supplies such as switched mode power supplies. The usage of these modern supplies may reduce the analog signal quality dramatically!

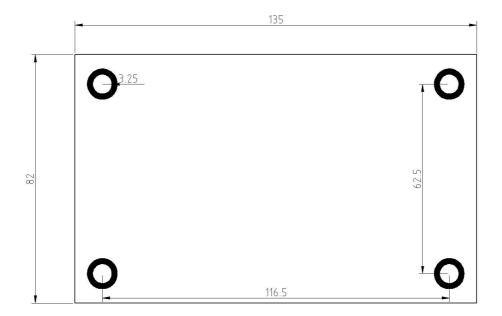

The layout of the drills of the original power supply is given in Figure 8.

Figure 8: mechanical Layout of the stand alone transmitter power supply

#### **Maintenance of the Transmitter**

Under normal circumstances the Viplax-I transmitter requires no maintenance. Merely, if the supply voltage polarity has been connected in a wrong way, it is possible that the transmitters internal fuse got blown and must be replaced. The fuse is the F1 on the PCB (PicoFuse). See also the layouts in the attachment to this document.

If the transmitter is not connected to a fiber optic line, a cap should protect the optical subsystem to avoid any damage.

Do not touch the fiber optic connector at its 'Ferrule'. If Viplax-I is not used, please cover the Ferrules with a dust caps.

# Viplax-I Transmitter (Eurocard version)

The eCard version of the Viplax-I transmitter is a 3U unit for 19" rack-mount systems. This version of the transmitter is basically the same as the handheld version. Therefore it is a good idea to read the specification of the handheld Viplax-I first. However there are differences which we will describe in this section of the handbook.

# The Orientation of the Comparator DIP switches

The layout of the eCard transmitter is of course different to the handheld versions. Therefore the placement of the DIP switches for the comparator settings is different as the following figure illustrates.

Figure 9: Orientation of the comparator DIP switches

## The used Power Supply

The power supply you want to use is from the same kind as the one for the Viplax-I receiver (see Power Supply for the Receiver). To interconnect the power supply and the Viplax-I eCard you will additionally need a backplane. Again you can use the same as we offer for the Viplax-I receiver (see Backplane Basic and Basic-Bi).

#### Additional I/O

Like Viplax-I handheld, there are additional I/Os available on the VG connector X5. These are dedicated for system enhancements (please contact Inventronik GmbH for usage). The table 7 below shows their usage.

| connector Pinof X5 | Function                                |

|--------------------|-----------------------------------------|

| X5-A1              | Monitor (1)                             |

| X5-A17             | Comp (Output fo the digital comparator) |

| X5-A18             | GPIO                                    |

| X5-A19             | GPIO                                    |

| X5-A20             | GPIO                                    |

| X5-A21             | GPIO                                    |

| X5-A22             | GPIO                                    |

| X5-A23             | GPIO                                    |

| X5-A24             | Thermo (2)                              |

| X5-C3 – X5-C15     | Gnd                                     |

| X5-C18 – X5-C30    | Gnd                                     |

Table 7: Additional I/O

The Thermocontact 'Thermo' is a supervision of the temperature of the Viplax shunt, which is separately available as an accesoire. The contact is normally closed and therefore a low indicates no error. The input on the eCard is equipped with a pull up resistor. If there is another sensor than the shunt connected to the Viplax-I eCard transmitter, there must be taken care of shorting the 'Thermo' input and ground. The connector is illustrated in the following section. Thus pins 2 and 4 of this connector must be shorted or another appropriate sensor must be connected. Otherwise the eCard indicates a fault.

The 'Thermo' contact is combined with the fault signal LOW\_BAT for there is never a LOW\_BAT in the eCard and there is no 'Thermo' contact in the handheld. The error handling is therefore the same as for the LOW\_BAT signal in the handheld version.

<sup>(1)</sup> Is a mirror of the input signal equipped with an impedance converter with a max. output voltage of 2.5V (max. output current 20mA).

<sup>(2)</sup> This signal is active high.

# **Analog Input or Sensor Plug**

This connector is compared to Viplax-I handheld more flexible. Besides the analog input there is also a digital input signal and a supply voltage of +/-15V. This makes it possible to connect additional special purpose sensors like the Viplax-I Shunt-100A. The port connector is Lemo 0B-5. It is located on the front panel of Viplax-I eCard. Figure 10 shows the front view of the female plug.

Figure 10: Lemo 5B-2

| Pin 1 | Analog input            |

|-------|-------------------------|

| Pin 2 | Digtal input (max. 15V) |

| Pin 3 | +15V                    |

| Pin 4 | Gnd                     |

| Pin 5 | -15V                    |

table 8: Front panel female plug.

# Viplax-I Receiver

Figure 11: Viplax-I Receiver.

#### **Technical Description**

Digital data processing goes vice versa, compared to the transmitter. The received serial data stream will be converted into parallel equivalent. Transmission check bits indicate a valid reception. Next the system check bits and the user-bit GP\_BIT7 are extracted (see attachments: connector X6 pin number 8, (D\_OUT1).

The remaining parallel data is converted back to an analog signal. Two output amplifiers provide the desired output signal conditioning. The analog output is available on two output connectors. Both outputs are capable to drive 50 Ohm loads (BNC jack and SM jack). The maximum output voltage swing is +/-10V for the BNC jack and +/-5V for the SM jack.

Viplax-I receivers are equipped with a microcontroller system board which provides the control and supervision of the digital data processing. Communication with a host computer is available through a USB- or TCP/IP ethernet interface (depending on the type of the Viplax-I receiver).

The highspeed digital data processing is implemented in a field programmable gate aray (FPGA), which is a custom design.

Both, the microcontroller unit and the FPGA unit are separate modules pluggable to the Viplax-I system board. The microcontroller unit is either a MiniFlex-USB module (USB version) or a ARM7TDMI embedded Linux (TCP/IP version) from FS-Forth Systems. The FPGA is a Sphinx-C100-RevA2 module. Further informations can be found in the chapters concerning the software configuration.

The receiver comes in euroboard form factor. All digital signals are connected to headers and/or 64 pin (a+c) VG type connector. The printed circuit board is installed in a 3U, 10HU plug-in case.

#### **Functional Description of the Error Logic**

Viplax-I includes a fast error detection logic with a total response time of about 1,5µs (inclusive data transmission from the transmitter to the receiver). This system exists of two separate subsystems, the **error processing system** and the **first fault memory**.

#### **Error Processing System**

Transmitter and receiver errors will be collected and processed by this instance. The error processing system is optimized and needs only several system clock cycles (about 100ns). Compared to the total response time, the error handling is almost negligible.

The description of the error system behaviour and the resulting system status is described as follows. All signals are 'active high':

- LOW\_BAT: This error signal is caused by the transmitter. The signal is connected to the output D\_OUT2 (connector X6, pin 7). It is also an input to the first fault memory.

- **COMP\_FLT:** This error signal is caused by the transmitter. The signal is connected to the output D\_OUT3 (connector X6, pin 6). It is also an input to the first fault memory.

- **AD\_FLT:** This error signal is caused by the transmitter. The signal is connected to the output D\_OUT4 (connector X6, pin 5). It is also an input to the first fault memory.

- LINK\_FLT: This signal indicates a fiber optic error. It is asserted in case of a not installed or faulty fiber optic cable. Other reasons are the damage of the optical subsystem in transmitter or receiver component. A LED on the front panel will indicate this error. Furthermore it is an input to the first fault memory and, in combination with the enable status of the microprocessor, connected as LINK\_RDY to D\_OUT5 (connector X6, pin4).

- LINK\_RDY: This status indicates the standby of the Viplax-I transmission system. LINK\_RDY is deasserted if a LINK\_FLT is asserted or if the microcontroller is in configuration process e.g. changing comparator thresholds to the FPGA. Right after power up or after a system reset, the signal is suppressed for about 300ms to guarantee the correct initialisation of the internal phase locked loop circuits. The signal is connected to the output D\_OUT5 (connector X6, pin 4).

- COMP\_1L, COMP\_1H, COMP\_2L, COMP\_2H: are the upper respective lower thresholds of the both receiver comparator units. These signals are not connected to any outputs but used as inputs to the first fault memory.

If desired, the error detection system can be disabled. However this has also an effect to the first fault memory, since these errors are not available anymore.

The only exception is the LINK\_FLT signal which is always enabled to guarantee a reliable supervision of the fiber optic line.

#### **Link Synchronisation**

The Viplax system is with firmware 2.8 or up equipped with a link synchronisation state machine. This feature helps syncing the link during the startup sequence and works as follows:

If the Viplax system is turned on, the receiver detects the incoming data of the transmitter and

synchronizes it until a valid data connection is established. After the link is stable, the behaviour of the state machine depends on enabling the resynchronisation or not (EN\_RESYNC). If it is on (enabled), the link synchronizes every time, the data gets invalid. If the EN\_RESYNC is disabled, the synchronisation will never take place for a second time. In both cases, the link fault is unaffected of EN\_RESYNC and is stored in the first fault memory in any case. It can be cleared by clearing the faults via the maintenance software or the dedicated pin on the backplane.

Figure 12: Viplax-I Receiver (front view).

#### First Fault Memory

The First Fault Memory sub-system is responsible for storing errors. If an error occurs there might be a lot of consecutive errors as result of the initial fault. Since these consecutive errors are just a side effect the system masks them out. Only the first fault is stored.